问题背景

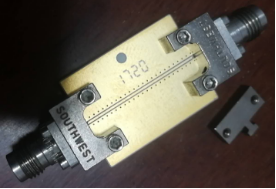

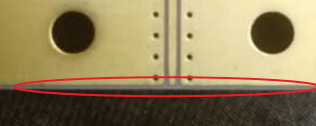

近日笔者设计了一款50GHz的板边安装射频连接器测试板,安装完成后如图1所示。

图 1 50GHz板边安装射频连接器测试板

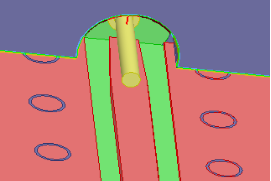

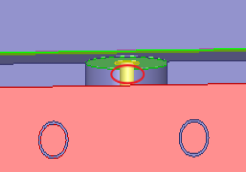

为了更好的阻抗连续性,在射频连接器管脚到PCB过渡位置做了Taper,Taper位置的仿真模型如图2左侧所示,一通优化猛如虎,最后的TDR仿真结果如图2右侧所示,一切看起来都是那么完美,笔者兴冲冲的就去投板了。

图 2 PCB信号Taper模型(左侧)及原始测试板TDR仿真结果(右侧)

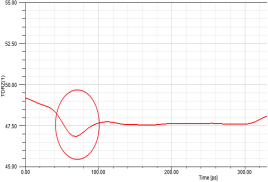

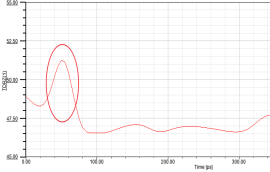

回板,安装,测试,一盆凉水从头浇下来,测试结果显示带宽只有约30GHz(回波损耗不超过10dB位置),TDR结果显示罪魁祸首就是连接器和PCB的过渡位置,呈现明显的感性阻抗,大约56欧姆,如图3所示。笔者当时就有些懵逼,这不科学啊,哪里出了问题呢?

图 3 原始测试板TDR测试结果

问题定位

笔者首先觉得会不会是安装问题,挂着网络分析仪进行了一番拆拆装装,收效甚微,暂时排除了该问题;然后对着模型挨个检查,也没有发现任何异常;笔者还想测量一下板厂加工的taper精度是否足够,由于没有显微镜,暂时放弃了。

既然没有找到快速解决的办法,笔者点了一根烟,开始思索起来。仿真略带一点容性,实测就转换为感性,引入该问题只有两种可能性,第一,仿真结果出现偏差,taper做过了(15mil线宽taper到11mil),根据经验,笔者认为可能性极小;第二,连接器中心导体和PCB接触不够紧密,有裸露部分。笔者仔细观察了一下PCB的板边部分,如图4所示,果然有线索。从图中可以清晰的看到大约有零点几毫米的无铜部分,估计这就是问题所在。

图 4 PCB板边无铜部分细节

既然有了怀疑对象,笔者开始尝试仿真复现该现象,在模型中将连接器和PCB板边改为非紧密接触,在水平方向互相拉开10mil的距离,这样可以人为制造10mil的中心导体裸露区,如图5左侧所示,TDR仿真果然看到了3欧姆左右的感性阻抗抬升,如图5右侧所示,和实测结果基本一致。

图 5 模型构造中心导体裸露区(左侧)和中心导体裸露10mil TDR仿真结果(右侧)

问题修改

捞起锉刀对着板边一阵猛搓,直到铜边与板边齐平,重新安装连接器。

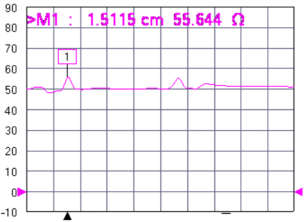

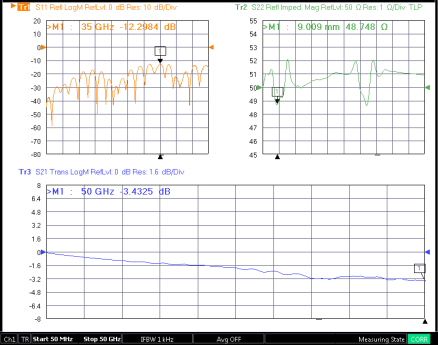

回归测试

结果是非常的Amazing啊,阻抗瞬间就降到52欧姆了,带宽哗哗的就到50GHz了,问题解决,yeah!

图 6 修改后测试板插损、回损和TDR结果

思考

后续如何避免该类问题呢?个人觉得方法如下

Ø 设计上需要保证板边与铜边齐平;

Ø 加工上需要和板厂确认不做削铜处理;