6Gbps SerDes EVB设计方案

-

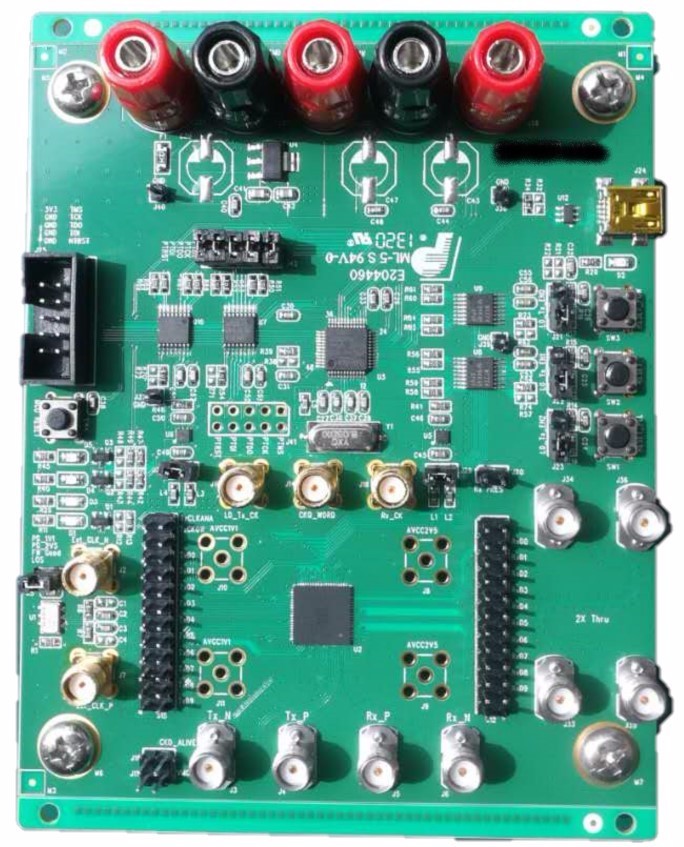

6Gbps SerDes EVB设计方案(1/2)

-

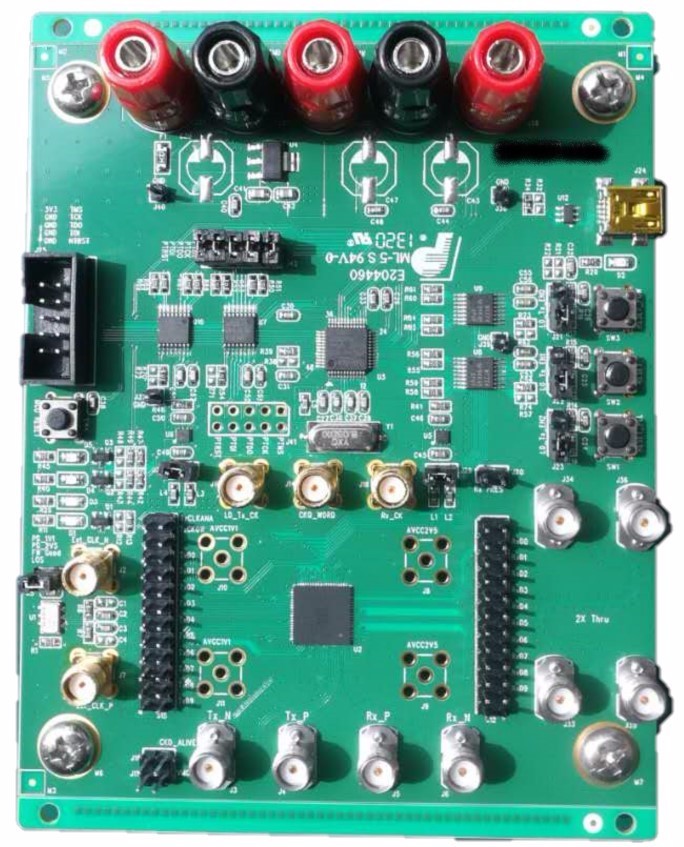

6Gbps SerDes EVB设计方案(2/2)

应用背景:

某客户DUT为一颗6Gbps SerDes芯片,客户已有EVB(Evaluation Board测试板),为深圳某公司设计,使用FPGA作为控制器,客户痛点如下:

高速信号使用Edge mounting SMA连接器,按理阻抗应该很好,但是TDR测试结果显示连接器部分阻抗为单端30欧姆左右,无法满足50+/-5欧姆需求;

原有方案每次寄存器读写均需要重新烧录fpga,客户反馈非常不方便;

解决方案:

为该客户重新开发了EVB,做了以下改进:

使用侧面开槽的SMA连接器,使用共面波导传输线设计高速信号线,优化了连接器和芯片管脚处阻抗;

使用mcu作为控制器,USB作为PC控制接口,设计了mcu和SerDes芯片的通信协议以及mcu和PC的通信协议;

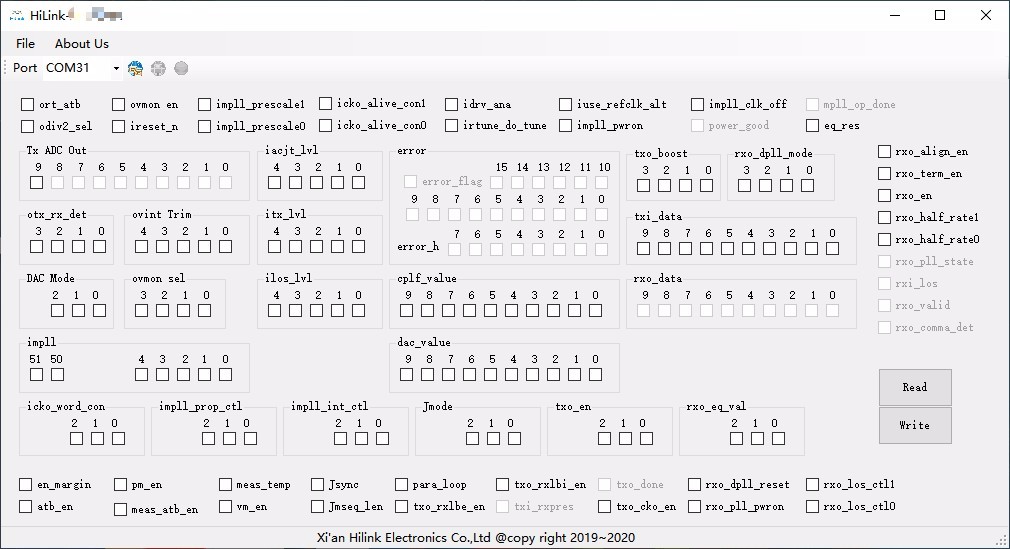

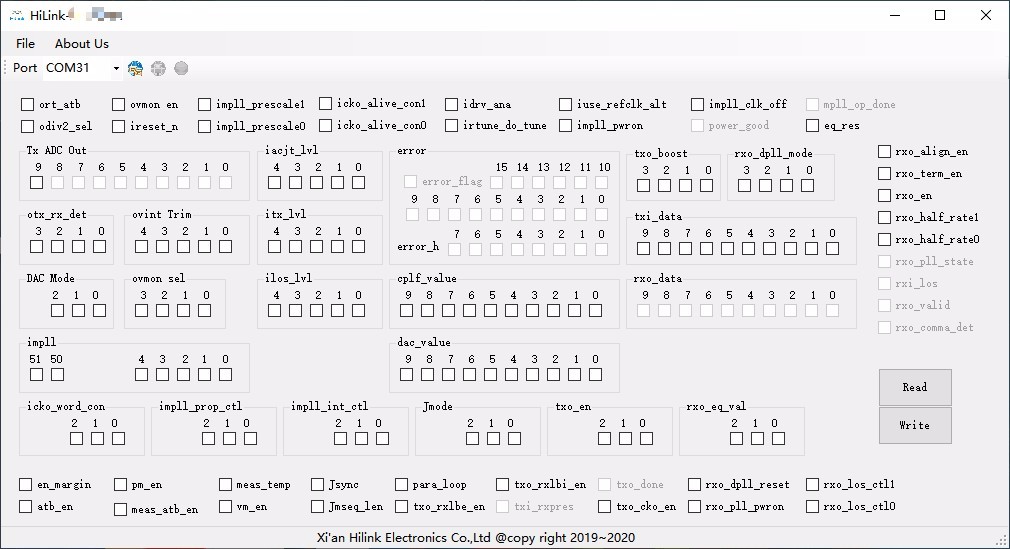

设计了GUI(图形用户界面),方便客户在PC端直接进行芯片的寄存器读写,而不需要任何其他程序收录;

设计了可选的SerDes外接电源供电,方便客户做调压测试使用;

总结:

基于客户当前痛点,运用我们擅长的高速电路板设计技术及mcu系统设计经验,帮助客户实现了一套非常简洁且成本远低于原方案的EVB方案,成功解决了高速信号的阻抗和寄存器读写需要烧录fpga的问题。

由于客户芯片也是工程样片,且通信协议为私有协议,为了保证一次性交付成功,我司主动承担成本专门投了一版验证板用于芯片通讯协议验证及芯片功能验证,事后证明非常有必要,在验证板上发现了几个重要问题,和客户确认并解决后改投正式EVB,一次性交付成功,客户满意度高。